Logitech a annoncé une nouvelle souris la semaine dernière. Un représentant de l'entreprise a contacté Ars de Logitech pour lui présenter sa «dernière souris sans fil». l'outil Page produit Il lit le même écrit.

J'ai eu une bonne expérience avec les souris Logitech, notamment celles sans fil, dont j'utilise actuellement une. J’avais donc hâte de voir ce que Logitech aurait pu faire pour améliorer ses précédentes conceptions de souris sans fil. Un clic plus silencieux ? Une nouvelle forme qui s'adapte mieux à ma main droite surmenée ? Plusieurs profils combinés dans un design prêt pour l'entreprise ?

J'ai été déçu d'apprendre que la caractéristique la plus unique du Logitech Signature AI Edition M750 est le bouton au sud de la molette de défilement. Ce bouton est précédemment programmé pour lancer le générateur de messages ChatGPT, que Logitech a récemment ajouté à son application de configuration de périphériques Options+.

C'est à peu près tout.

De plus, le M750 ressemble exactement au Logitech Signature M650, introduit en janvier 2022. Le bouton avant de la nouvelle souris (sur le côté gauche de la souris) est préprogrammé pour exécuter Windows ou macOS, et le bouton retour s'ouvre. ChatGPT est dans Options+. Au moment d'écrire ces lignes, le PDSF de la nouvelle souris est supérieur de 10 $ (50 $) à celui de la M650.

-

Le nouveau M750 (photo) mesure 4,26 x 2,4 x 1,52 pouces et 3,57 onces.

Logitech

-

Le M650 (photo) est disponible en trois tailles. La taille moyenne est de 4,26 x 2,4 x 1,52 pouces et 3,58 onces.

Logitech

J'ai interrogé Logitech à propos du M750, qui semble être le M650 mais avec un bouton supplémentaire, et un porte-parole a déclaré :

La M750 n’est pas en réalité la même souris que la M650. Il dispose d'un bouton préprogrammé supplémentaire pour lancer Logi AI Prompt Builder une fois que l'utilisateur a installé l'application Logi Options+. Sans Options+, le bouton fait basculer le DPI entre 1 000 et 1 600 DPI.

Cependant, un bouton au sud de la molette de défilement de la souris qui peut être programmé pour lancer une application ou basculer le DPI est très courant, y compris parmi les souris Logitech. Un représentant de Logitech m'a également affirmé que les deux souris utilisaient des composants électroniques différents, que Logitech appelle la plate-forme de la souris. Logitech peut réutiliser les plates-formes pour différents modèles, a indiqué le porte-parole.

Un représentant de Logitech a refusé de commenter pourquoi il n'y a pas de bouton au sud de la molette de défilement sur le M650. Le prix est une raison possible, mais Logitech vend également des souris moins chères dotées de cette fonctionnalité.

Cependant, les différences mineures entre les deux suggèrent que le M750 ne mérite pas une version complète du produit. Je soupçonne que sans la nouvelle fonctionnalité logicielle tendance de Logitech, le M750 n'aurait pas été présenté comme un nouveau produit.

Le M750 soulève également la question de savoir combien de périphériques d’entrée informatiques doivent être équipés d’une sorte de fonctionnalité de génération d’IA.

Générateur GPT de chat instantané Logitech

La version beaucoup plus importante de Logitech la semaine dernière n'était pas une version marginale mais un ajout à son application Options+. Vous n'avez pas besoin de la « nouvelle » souris M750 pour utiliser AI Prompt Builder de Logitech ; J'ai pu programmer le MX Master 3S pour qu'il fonctionne. plusieurs Les souris et claviers Logitech prennent en charge AI Prompt Builder.

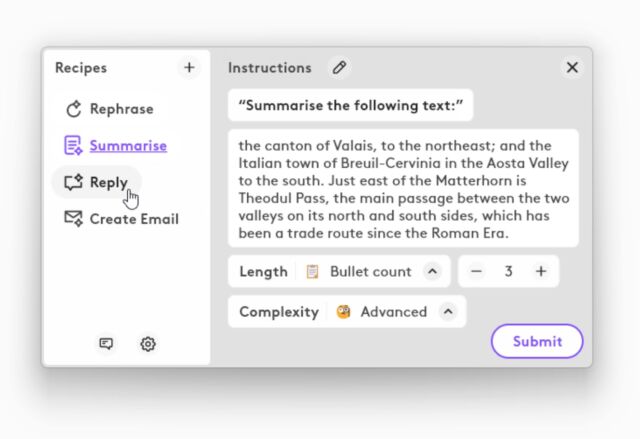

Lorsque vous appuyez sur un bouton qui lance le générateur d'invites, la fenêtre Options+ apparaît. Là, vous pouvez saisir le texte que Options+ utilisera pour créer une invite ChatGPT appropriée en fonction de vos besoins :

Logitech

Après avoir fait vos choix, une autre fenêtre s'ouvre avec la réponse ChatGPT. Logitech a déclaré que l'outil de création instantanée nécessite un compte ChatGPT, mais j'ai pu utiliser GPT-3.5 sans en saisir un (la fonctionnalité peut également fonctionner avec GPT-4).

Un Arsien typique n'a probablement pas besoin d'aide pour créer une invite ChatGPT, et la nouvelle fonctionnalité de Logitech ne fonctionne avec aucun autre chatbot. L'Instant Builder pourrait être intéressant pour les personnes moins expérimentées techniquement et intéressées par certains utilitaires pour les premières expériences ChatGPT. Cependant, je doute que les personnes ayant une compréhension rudimentaire de l’IA générative aient besoin d’un accès immédiat à ChatGPT.

Cependant, le point important est l'accès instantané aux fonctionnalités de ChatGPT, ce qui, selon Logitech, est utile pour ses utilisateurs expérimentés. quelques Logitech ClientMalgré ça, Il semble Je ne suis pas d'accord, surtout avec AI Prompt Builder, ce qui signifie que Options+ a plus de ressources En arrière-plan.

Mais Logitech n'est pas la seule entreprise de gadgets à vouloir lier l'accès IA à un bouton matériel.

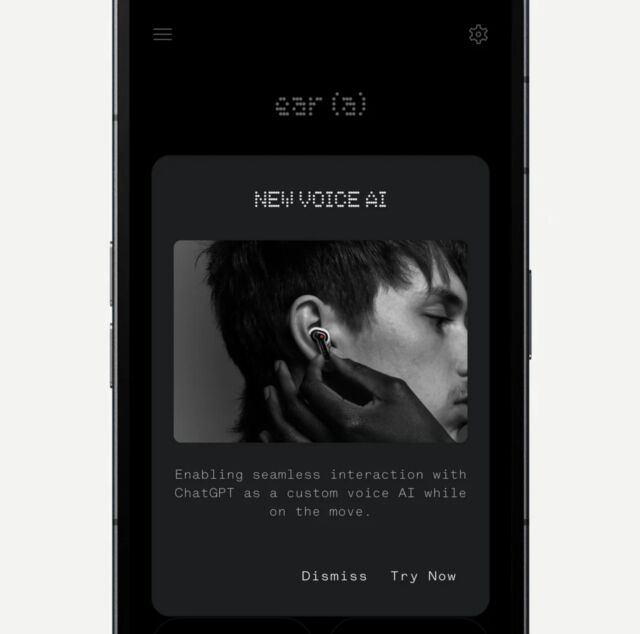

Appuyez sur les écouteurs pour parler à ChatGPT

Comme Logitech, Nothing n'essaie pas de donner à ses clients un accès rapide à ChatGPT. Dans ce cas, l'accès s'effectue en appuyant sur l'appareil. Nothing a annoncé ce mois-ci avoir « intégré les écouteurs Nothing et Nothing OS avec ChatGPT pour fournir aux utilisateurs un accès instantané aux connaissances directement à partir des appareils qu'ils utilisent le plus, comme les écouteurs et les smartphones ». Cette fonctionnalité nécessite le dernier système d'exploitation Nothing et que les utilisateurs disposent d'un téléphone Nothing avec ChatGPT installé. Les gestes ChatGPT fonctionnent avec Nothing's Phone (2), Nothing Ear et Nothing Ear (a), mais Nothing prévoit de s'étendre à des téléphones supplémentaires via des mises à jour logicielles.

rien

Il ne dit pas non plus qu'il inclurait des « points d'entrée au niveau du système » à ChatGPT, tels que le partage de captures d'écran et « aucun élément d'interface utilisateur » dans les systèmes d'exploitation des smartphones.

L'intégration de ChatGPT ne serait rien moins intrusive que l'intégration de Logitech puisque les utilisateurs qui n'ont pas ChatGPT sur leur téléphone ne seront pas affectés. Mais, encore une fois, vous vous demandez peut-être combien de personnes ont demandé cette fonctionnalité et quelle est sa fiabilité pour son fonctionnement.